| 學程簡介 | 課程大綱 | 課程預覽 | 會員優惠 |

➤ 獨家資深業師授課!提供課程答疑平台,訓中訓後為學員排難解惑。

📌 本課程可申請補助:大人提、小人提、退輔會補助適用

AI 深度學習、5G 傳輸高達 10Gbps、無人駕駛要求延遲小於 1ms

這些已無法再只依靠 CPU 完成...

為了突破雲端運算在頻寬、延遲、儲存與資安上的侷限,邊緣運算崛起——

終端裝置被賦予了智慧與運算能力,硬體的關鍵價值再度被看見!

想要實現更高的運算效能與功耗性能、更低的延遲、更高的安全性,以及更短的開發週期?

FPGA晶片,正是實現這些目標的重要解決方案!

艾鍗學院特別邀請具有16年以上FPGA開發經驗的一線資深工程師,精心規劃「FPGA數位IC設計實戰」課程。

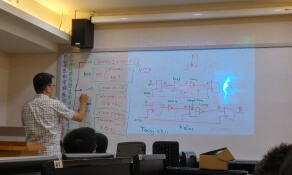

本課程以「從概念到實作」為核心,專為想扎實學會FPGA設計的同學設計。課程分成三個階段,第一階段從數位電路的基本原理出發,深入講解Verilog HDL與實際硬體邏輯的對應關係,讓學生能真正理解程式背後的電路行為。第二階段透過實作I2C、SPI、UART等常見介面電路,並搭配simulation與testbench驗證技巧,培養學生獨立除錯與驗證能力。最後第三階段,課程將引導學生使用Altera MAX 10 FPGA與NIOS-V處理器,體驗SoC FPGA的完整開發流程,從硬體設計、整合到系統應用,全面建立軟硬整合的設計思維與實戰能力。

因為真正實戰,所以好評不斷

講師持續結合業界前線經驗與艾鍗教學經驗,這段絕無僅有FPGA課程之旅將帶你:

✔奠定數位電路設計基石,理解並行運算邏輯,掌握Verilog HDL的核心概念與實用技巧。

✔瞭解業界流程,將理論知識應用於實際的FPGA晶片設計與除錯,建立從設計到驗證的IC設計工程師實戰力!

✔深入SoC FPGA嵌入式系統晶片開發,掌握硬體與軟體整合的完整解決方案,打造高性能SoC嵌入式系統。

Why SoC FPGA?

關鍵詞:

FPGA,SoC FPGA,Intel,Altera,Intel Quartus Prime,MegaWizard,Qsys,ModelSim,HDL,Verilog,

MAX 10,Avalon,AXI,IP Core,TestBench,Terasic T-Core,CPLD,Linux Driver,NIOS-V

Jemmy (講師具16年數位IC設計經驗)

▪ 電機工程碩士 ▪ 資深數位IC設計工程師

▪ FPGA/CPLD設計 ▪ Verilog HDL ▪ Gigabit Ethernet網路介面訊號處理

▪ FPGA SoC系統設計 ▪ 數位電路分析設計 ▪ 數位晶片產品開發

─ 演算法與架構並存的時代,用FPGA以更快的速度把產品做出來

Ted Chang (講師具16年數位IC設計經驗)

▪ EE工程碩士 ▪ 資深數位IC設計工程師

▪ FPGA/ASIC設計 ▪ RTL Design, FPGA Validation ▪ 系統晶片設計與整合

▪ Gigabit Ethernett, TDM over IP, video over data design

▪ ARM SOC AXI/AHB/APB ▪ IC電路模擬測試 ▪ Verilog /VHDL

─ 雖然資深但是不間斷Learning

-

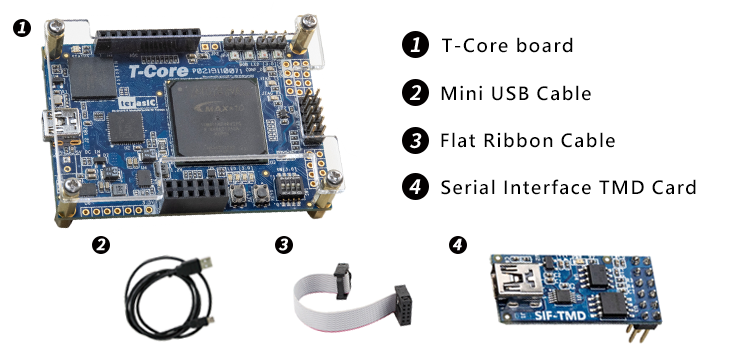

Altera MAX 10 FPGA:T-Core

▪ Programmable FPGA元件

- MAX 10 10M50DAF484C7G 元件

- 集成雙ADC,每個ADC支持1個專用模擬輸入引腳和8個雙功能引腳

- 50K 邏輯單元

- 1638Kb M9K 塊

- 144 个 18x18 乘法器

- 4 個鎖相環

▪ 通用介面

- 4 個綠光 LED

- 4 個紅光 LED

- 4 個滑動開關

- 2 個去抖動按鈕

▪ JTAG

- 板載USB Blaster II下載電路用於下載MAX10

- 板載USB Blaster II下載電路用於下載RISC-V 程式

- JTAG Master功能用於下載別的板子上的FPGA

▪ Clock與記憶體元件

- 兩個50 MHz Single-ended,外部 Oscillator Clock源

- 一個10 MHz Single-ended,外部l Oscillator Clock源

- 64Mb QSPI Flash (用於儲存 RISC-V 程式)

▪ 擴充介面

- 2x6 TMD 擴充接頭

- 1x10 ADC 接頭

- 兩個 1x3 RGB LED 擴充接頭

▪ 電源供應

- USB Type mini-AB Port (5V)

- 2-pin 擴充電源接頭 (4.4-5.6V)

▪ 連接性

- 連接 BTS-TMD

- USB-Blaster II 下載線

- 連接 WS2812B LED Strip

2、理解Verilog HDL與硬體邏輯電路之間的對應關係。

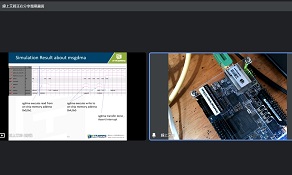

3、熟悉Testbench撰寫與模擬(Simulation)的流程,學會在燒錄前驗證設計正確性。

4、實作I2C、SPI、UART等常用週邊介面,強化實務設計能力。

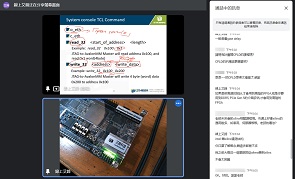

5、學會設定並應用Timing Constraint,確保設計在時序上正確運作。

6、掌握Platform Designer的使用,整合多個IP模組進行系統化設計。

7、熟悉System Console的除錯技巧,能有效分析與驗證硬體行為。

8、透過NIOS-V MCU實作,了解SoC FPGA的軟硬整合概念。

9、培養從邏輯設計、模擬驗證到系統整合的完整開發能力。

想熟悉Verilog HDL數位電路設計與數位訊號處理。

想熟悉Verilog HDL數位電路設計與數位訊號處理。 想熟悉ASIC/FPGA chip integration Synthesis/Compile/Simulation。

想熟悉ASIC/FPGA chip integration Synthesis/Compile/Simulation。 具MCU或嵌入式系統開發經驗,但你覺得市面上沒有你要的解決方案,所以想要了解並學習如何客製化開發IC。

具MCU或嵌入式系統開發經驗,但你覺得市面上沒有你要的解決方案,所以想要了解並學習如何客製化開發IC。 電子、電機 、資訊、通訊工程、自動控制與半導體等相關背景(或本身具數位邏輯基礎)。

電子、電機 、資訊、通訊工程、自動控制與半導體等相關背景(或本身具數位邏輯基礎)。FPGA研發設計工程師 | 數位IC設計工程師 | FPGA/RTL驗證工程師 | CPLD研發工程師 | 電信/通訊系統工程師| 多媒體數位視訊解碼晶片設計工程師

※104人力銀行調查: 數位IC設計工程師類薪資